Process corner detection by skew inverters for 500 MHZ 2×VDD output buffer using 40-nm CMOS technology - ScienceDirect

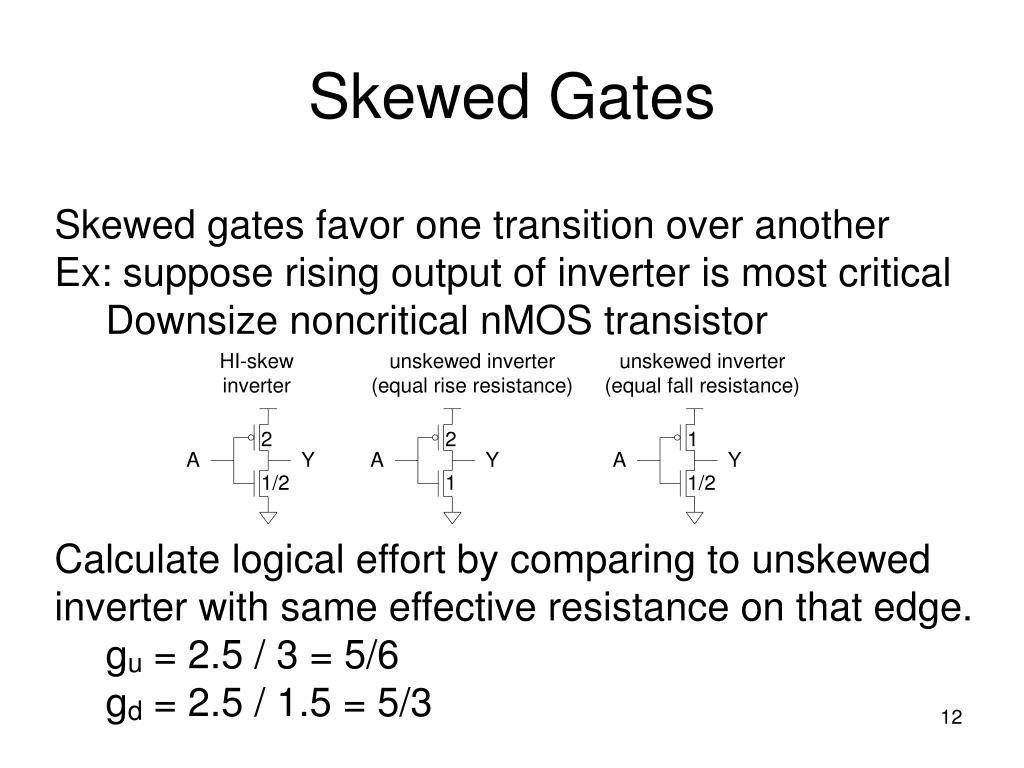

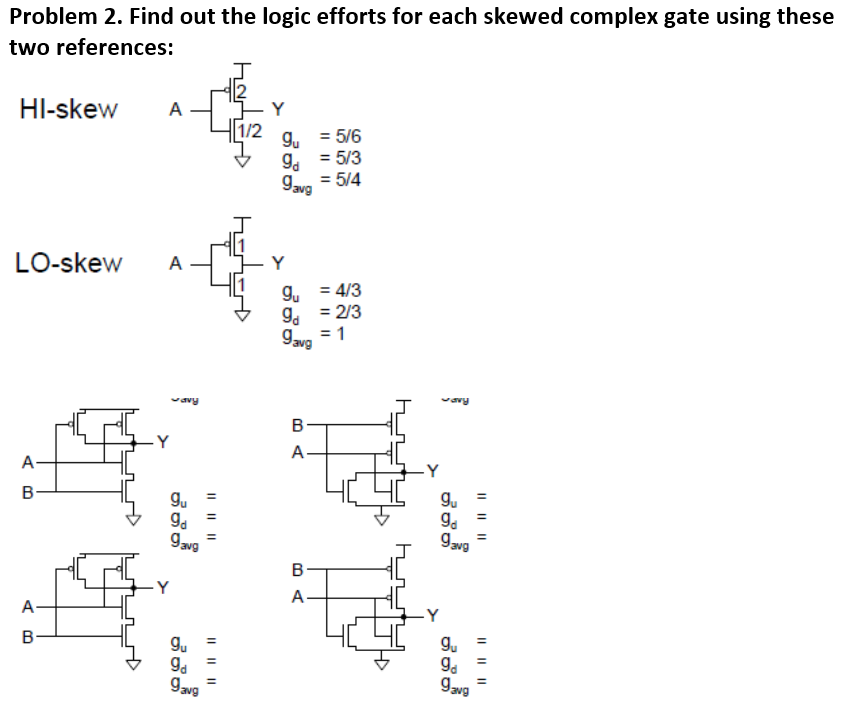

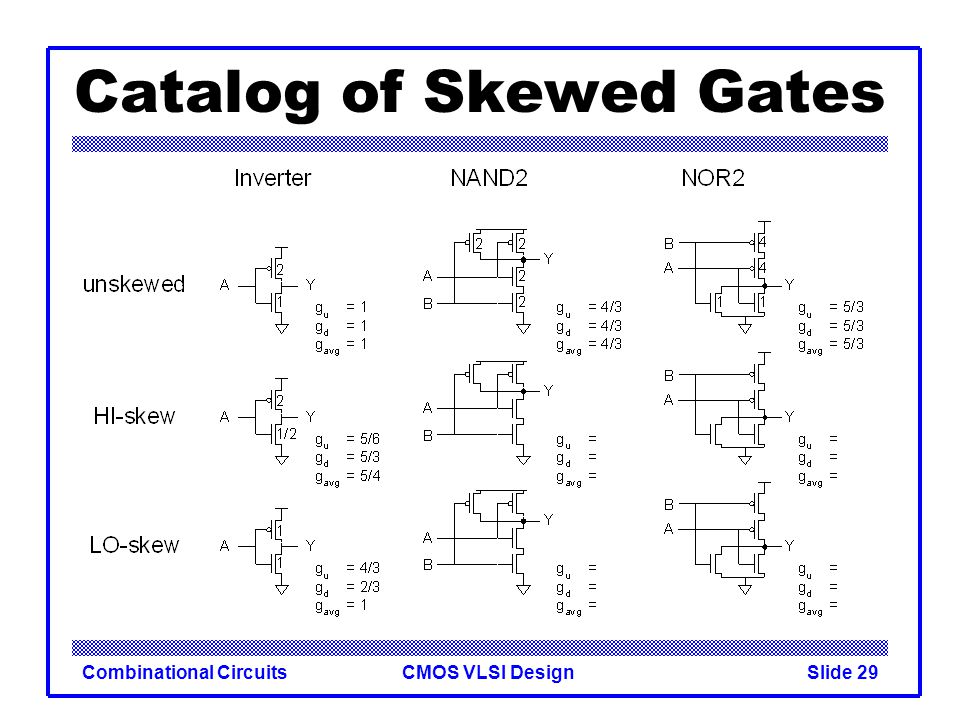

Solved] Design (find the size of NMOS and PMOS transistors) a skewed CMOS inverter that has a rising-edge logical effort (gu) four times smaller tha... | Course Hero